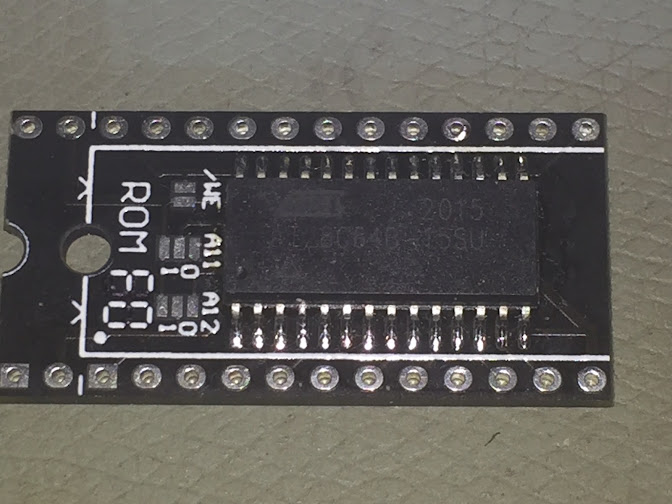

ET-3400 ROM - Program Test Video and Final Blog Post.

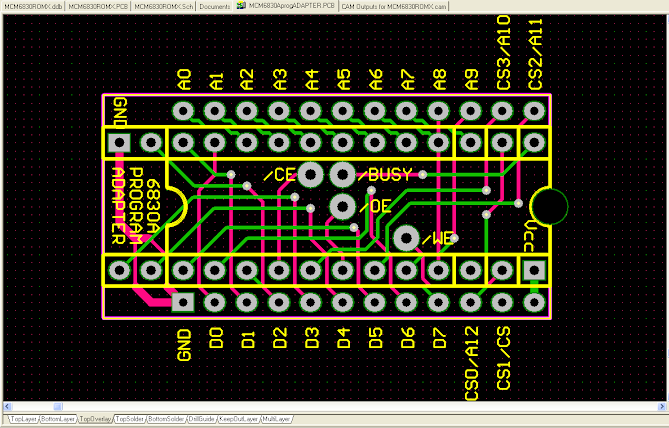

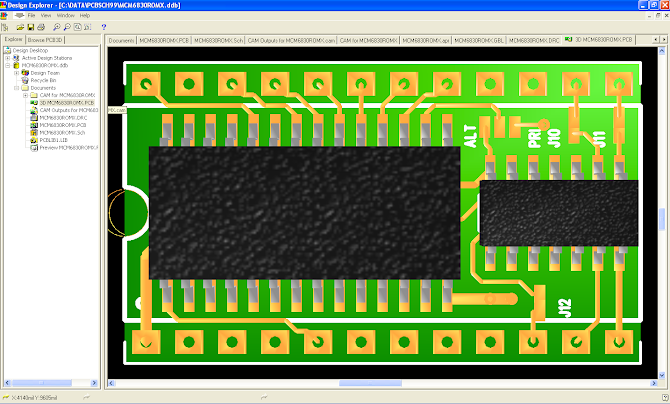

Resulting output from the program running on the ROM Replacement breadboard prototype with the patched ROM. Some characters in the alphabet are not possible to display on 7-segment displays, so you'll have to use your imagination a bit. Read the assembler listing in the previous post if you can't read it. While my RetroChallenge entry is complete, I still have to get PCBs manufactured and finish designing the adaptor PCB. Any further information on my progress will be posted on the groups.io/ET-3400 web site. Mark C.